|

Notre magasin (/fax: 061/32.00.15 Rue Albert 1er, 7 B-6810 Pin - Chiny |

Cours HARDWARE 1 d'YBET Informatique |

| FORMATIONS | Le MAGASIN YBET | PRODUITS et SERVICES |

| Définitions des termes techniques | Rayon d'action | |

| Dépannage PC et informatique | Plan d'accès |

| YBET informatique | CONTACT |

7.a. Structure des processeurs Athlon 64

7.a.1. Introduction - 7.2. Architecture standard des Athlon 64, 64 FX et Opteron - 7.a.3. Architecture interne des Athlon 64

Dans le chapitre précédant, nous avons l'architecture interne des processeurs courants. Nous verrons dans ce chapitre l'architecture des Athlons 64 bits (Athlon 64 - Athlon FX et Opteron). Même si le coeur du processeur semble équivalent, les différents modèles diffèrent principalement par leurs composants externes. Pour les caractéristiques des processeurs AMD-64 (vitesse effective, FSB, ..).

Cette famille utilise une architecture interne mixte 32 - 64 bits. Ils sont donc capable d'utiliser des systèmes d'exploitation 32 bits (Windows 95/98/me/2000/NT/XP) et des système d'exploitation 64 bits (Linux, Windows 64 bits - XP ou les différentes versions équivalentes de Vista, Seven, ... 2003). Si Intel a créer de nouvelles instructions pour l'Itanium, AMD (suivi par INTEL avec le XEON et ensuite les Intel Core 2)) n'a pas fondamentalement changer l'architecture. Elle repose sur des registres au format 64 bits pour les instructions et données mais dans ce cas, elles ont été simplement allongées (ce qui explique la compatibilité avec les instructions 32 bits). La limitation précédente à 32 explique notamment la limitation mémoire des 4 GB (2 32). En passant en 64, cette limitation n'existe plus. D'autres instructions passent également en 1 seul cycle d'horloge sur le bus au lieu de 2, d'où une augmentation de la vitesse globale de l'ordinateur avec des versions de systèmes d'exploitation spécifiques pour Windows ou recompilées (Linux). Ces processeurs se basent sur le jeu d'instructions MIPS64™ (l'Itanium utilise l'IA64). En mode 64, quelques instructions ont été rajoutée, alors que des anciennes instructions X86 peu utilisées ont simplement été supprimées. Divers registres multimédia ont également été ajoutés pour les instructions SSE.

Le microprocesseur Itanium d'Intel utilise uniquement une architecture 64 bits spécifique, il ne peut donc utiliser que des systèmes d'exploitations 64 bits spécifiques, en gros les versions serveurs haut de gamme de Windows 2003 et 2008 à partir de la version entreprise.

7.a.2. Architecture standard des athlon 64, athlon 64FX et Opteron

Reprenons pour commencer l'architecture standard d'un athlon de la famille 64. Il est constitué de 2 parties: la partie processeur comme nous connaissons et la partie "Northbridge", anciennement inclus dans le chipset.

Le cache L2 varie suivant le processeur: 256, 512 ou 1 MB pour l'Athlon 64, 1 MB pour l'Athlon 64 FX51 et Athlon FX53 et Opteron. Par rapport à l'architecture K7, le pipeline passe de 10 à 12 niveaux.

Dans la partie "Northbridge", on va retrouver l'interface mémoire DDR, DDR2 (socket AM2) et DDR3 (socket AM3).. C'est la première différence entre les différents processeurs de cette famille. Les Athlon 64 gèrent un bus de donnée externe de 64 bits (socket 754), ou comme les FX et Opteron, un bus de données de 128 Bits (en fait 2 bus 64 bits dual Channel) sur un socket 939 ou AM2 et AM3. Comme ces processeurs gèrent les mémoires ECC, les Athlon 64 bits accepteront la mémoire ECC sur 8 bits de contrôle contre 16 bits-Ecc pour les autres.

La partie JTAG - Debug est liée à la difficulté de tester des circuits électroniques complexes. Cette méthode développée fin des années 80 permet de tester "de l'extérieur" le circuit électronique en mémorisant les valeurs d'entrées et sorties.. Elle n'est donc pas directement utilisée dans les PC.

L'Hyper transport est le bus rapide permettant la connexion entre le northbridge et le southbridge. Le nombre de canaux est de 1 pour les Athlons 64 et Athlons 64FX. Pour l'opteron, il est de 3 canaux. Chaque canal est capable de transférer 3,2 GB/s dans chaque sens (6,4 GB/s au total), plus dans les versions suivantes de ce bus inter-bridge.

Tout ceci explique notamment les différents socket pour la famille Athlon 64

- Athlon 64: socket 754, évolué mi- 2004 vers le socket 939 qui gère le Dual Channel

- Athlon 64 FX: socket 940 (identique à l'opteron), évolué mi- 2004 vers le socket 939 (identique à l'Athlon64). Les premiers Athlon FX51 étaient donc des Opteron avec 2 des trois canaux hyper transports désactivés. L'athlon FX53 redevient un Athlon 64 avec un cache plus important.

- Athlon Opteron: socket 940

- Le socket AM2 est spécifique aux versions utilisant de la mémoire DDR-2. Début 2008, il est remplacé sur les processeurs de haute gamme par l'AM2+, totalement compatible, un processeur utilisant la version + accepte une carte mère en version standard et vis versa. La différence vient du bus hypertransport qui passe de la version 2 (1,6 Ghz maximum) à la version 3.0 (2,6 Ghz maximum), à condition que le FSB du microprocesseur l'accepte bien sûr.

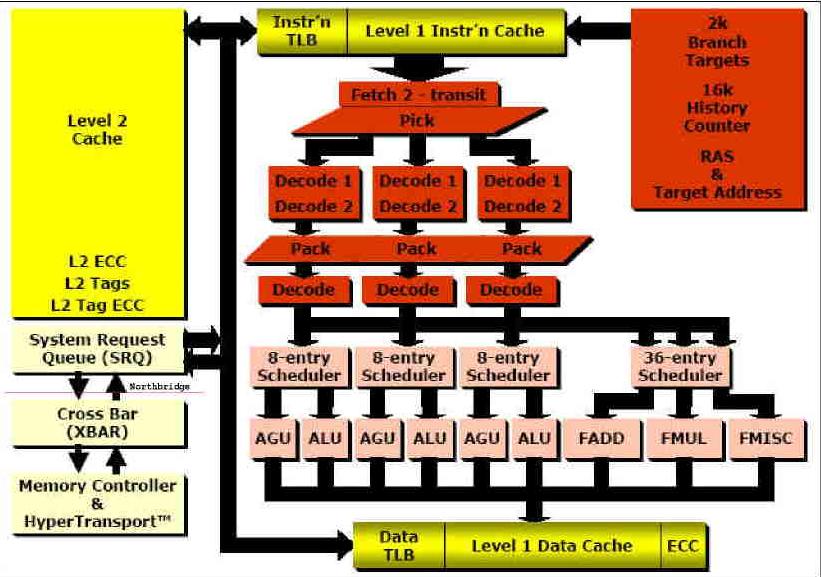

7.a.3. Architecture interne

L'architecture n'est pas en soit révolutionnaire. Les données sont envoyées et reçues de la mémoire via le contrôleur Hyper-transport et contrôleur mémoire à gauche. Elles sont envoyées soit le réservoir d'instruction. Le cache d'instructions L1 raccordé au circuit de prédiction de branchement permet également de fournir des instructions au processeur.

La partie en rouge rassemble le décodage du CISC vers RISC avec 3 niveaux de décodage. Les diverses parties internes sont identiques à celles que nous connaissons: unités de calculs ALU, AGU (Adress Generation Unit) pour les calculs sur des adresses, FADD (unité de calcul en virgule flottante), ...

Les données sont ensuite renvoyées soit vers le cache L1 correspondant, soit vers la mémoire.

Dans un sens, cette architecture n'est pas très différente de celle des Athlons XP ci-dessus (on s'en doutait un peu) mais ça devrait évoluer.

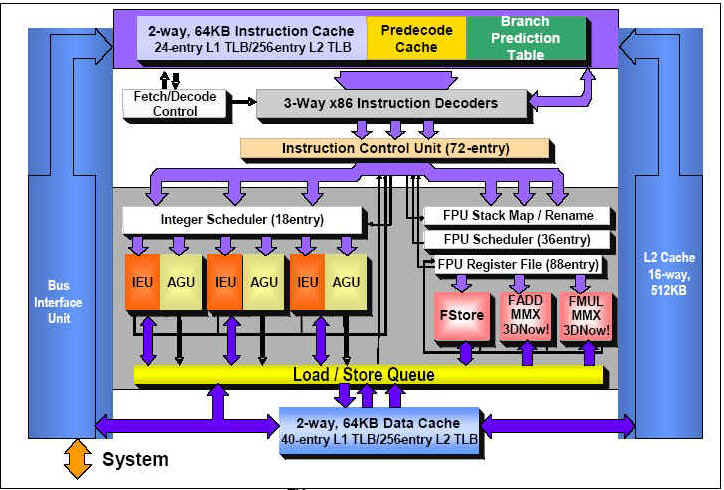

On retrouve de nouveaux d'un côté le bus de commande, données et adresses (Bus Interface Unit) et les données provenant du cache L2 (inclus dans le processeur). La partie au-dessus sert à prédécoder les instructions par 3 et inclut la table de prédiction de branchement. La partie suivante rassemble le passage des instructions CISC vers RISC et le transfert vers les différentes unités internes de l'Athlon XP.

|

La suite > 7.b. Architecture Netburst, Intel Core - 8. Chipset PC |

| < 7. Architecture processeur |

Dernière modification 18/09/2015

Cours techniques: Matériel informatique 1: PC et périphériques. Matériel informatique 2: réseaux, serveurs et communication - Systèmes d'exploitation Windows de Microsoft

Les compétences au service de la qualité.

Les activités d'YBET à Chiny