|

Notre magasin Rue Albert 1er, 7 6810 Pin - Chiny Route Arlon - Florenville (/fax: 061/32.00.15 |

Cours HARDWARE 1 d'YBET Informatique |

| FORMATIONS | Le MAGASIN YBET | PRODUITS et SERVICES |

| Dépannage PC et informatique | Activités et présentation | |

| Définitions des termes techniques | Plan d'accès à Pin |

| YBET | Cours hardware |

7. Structure interne des processeurs: architectures RISC, CISC, superscalaires, superpipelines, ...

7.1. Structure interne d'un processeur de base - 7.. Mémoire cache - 7.3. Passage du CISC au RISC - 7.4. Architecture pipeline, superpipeline et superscalaire - 7.5. Taille et alimentation des transistors - 7.6. Architecture interne des processeurs - 7.9. Conclusion.

Dans le chapitre 5, nous avons vus les différents microprocesseurs utilisés depuis le début des PC (familles, fabricants) et leurs caractéristiques techniques (fréquences internes, externes, ...). Le fonctionnement en détail de chaque processeur serait trop long à analyser, et surtout inutile. Nous allons simplement reprendre les différentes architectures internes par types. Ceci va nous permettre de comprendre les évolutions et les différences de performances entre des processeurs équivalents.

Le premier PC utilise le processeur Intel 8088. Pour assurer la compatibilité des programmes, les processeurs suivants utilisent les mêmes instructions en langage assembleur (un langage de programmation dédié aux microprocesseurs mais surtout spécifique à chaque famille). L'utilisation des mêmes instructions ne signifie pas qu'un nouvel ordinateur peut lire les anciens programmes, souvent à cause du système d'exploitation mais aussi parce que de nouvelles instructions ont été ajoutées pour dépasser la limitation de taille mémoire (1 MB pour un 8088), ajouter de nouvelles instructions multimédia (MMX, SSE, 3Dnow, ...), sans compter les versions 64 bits. Ces nouvelles commandes sont intégrées dans les langages évolués comme le C et finalement compilées en assembleur codés en hexadécimal.

Conserver les mêmes commandes que le 8086 pose quelques problèmes. Le premier vient de l'architecture interne du 8088 qui n'était pas franchement optimalisée. Les instructions sont d'abord codées par des commandes variant de 1 à 5 octets sans réelle organisation. Deux instructions peuvent utiliser le même contenu dans le premier octet et avoir des fonctionnalités complètement différentes. En plus, ces instructions reprennent des commandes rarement utilisées qui alourdissent le décodage et finalement ralentissent l'ensemble du traitement. Ces deux caractéristiques sont spécifiques aux processeurs utilisant des architectures CISC (Complex Instruction Set Computer) des premiers modèles. Ce type d'architecture interne est depuis une quinzaine d'année remplacée par des RISC (Reduced Instruction Set Computer). Ces processeurs n'utilisent plus d'instructions complexes (remplacées par plusieurs instructions plus simples) et fonctionnent plus rapidement. Pour garder la compatibilité avec notre vieux 8088, les processeurs PC chargent des instructions CISC et les recodent en instructions RISC avant d'exécuter les commandes.

7.1. Structure interne d'un processeur de base

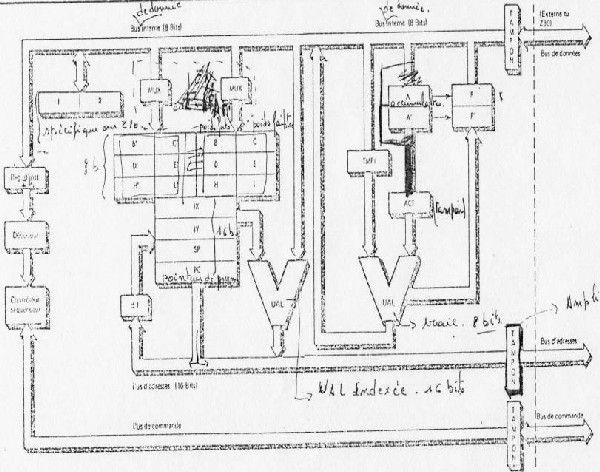

Au chapitre 3, nous avons utilisé le Z80 pour étudier les bus externes. Cette fois, nous allons voire son architecture interne, typique des premiers modèles, y compris du 8088.

Dans la partie supérieure du schéma ci-dessous, connectée au bus de donnée externe via un tampon, un bus de donnée interne. Dans la partie inférieure, de nouveau connexté à l'équivalent en externe, un bus d'adresse et un bus de commande. A droite, une unité (en anglais ALU pour Unit Arithmetic Logic, en français UAL pour Unité arithmétique et logique en Français) qui exécute des calculs simples sur des nombres entiers et des instructions logiques (AND, OR, ...) Cette UAL est connectée en entrée à l'accumulateur (une mémoire tampon avec le bus de donnée) et au bus de donnée (un simple buffer sert à authoriser l'entrée uniquement aux données qui doivent être calculées). En sortie, elle est directement connectée au bus de données.

Dans la partie centrale, on trouve des mémoires internes sur 8 bits (B, C, D, ...) et 4 mémoires sur 16 bits: IX et IY (indexes), PC (program Pointer) reprend l'adresse mémoire actuelle du programme et SP (Stack Pointer, pointeur de pile en français) qui permet de garder l'adresse courante du programme en cas de demande d'interruption. Toutes ces mémoires tampons sont appelés registres. Contrairement au 8088, le Z80 utilise des registres dédoublés (A', B', C', ...) qui perment de remplacer par multiplexage le registre correspondant.

Les 4 registres 16 bits sont relié à une deuxième unité de calcul plus simple que l'UAL qui permet d'effecter de petits calculs sur des adresses (notamment pour des saut de lignes genre aller à l'adresse +5). Ces registres d'adresses sont aussi reliés à un simple incrémenteur d'adresse (+1) pour le fonctionnement standard en assembleur, les instructions se suivent en mémoire. Tout à gauche, une partie permet la gestion du bus de commande: signaux de lecture - écriture, gestion des interruptions, ...

En abrégé, le schéma du Z80 devient:

Comme exemple de fonctionnement, prenons une instruction LDA BB qui charge le contenu de l'adresse BB dans l'accumulateur. Le bus de donnée étant de 8 bits, pour charger l'instruction, le Z80 va effectuer trois chargement mémoire (une pour l'instruction et deux pour l'adresse mémoire). Dans le Z80 comme dans le 8088, un seul cycle d'horloge est utilisé pour chaque chargement à partir d'une zone mémoire). Le chargement de l'instruction dans la partie décodage va donc utiliser 3 cycles d'horloge et une seule pour l'exécution. La grosse différence entre ces deux processeurs et la taille des registres puisque le 8088 utilise un bus interne de 16 bits.

Pour augmenter la vitesse de traitement interne de ce schéma, plusieurs solutions sont possibles.

- Essayer que le processeur revoivent des instructions à chaque cycle d'horloge, qu'il travaille tout le temps à pleine puissance.

- modifier la structure interne en chargeant les instructions CISC à partir de la mémoire (compatibilité avec les anciens programmes), les transformer en instruction CISC avant de les

- exécuter plusieurs instructions simultanément, ce qui en pratique dans cette architecture est difficile puisque les bus internes sont à chaque fois utiliser

- augmenter l'intégration des transistors en diminuant leur taille, ce qui augmente les vitesses de transfert en interne

- Optimaliser l'utilisation des bus internes et externes.

Toutes ces solutions sont utilisés pour optimaliser les processeurs par INTEL comme par AMD et d'autres.

7.2. Utilisation d'une mémoire cache

A partir du 486, la fréquence des mémoires devient inférieure à celle des processeurs. De fait, le point 1 de notre liste de possibilités d'ammélioration devient impossible. A partir du 486, les fabricants vont utiliser une mémoire cache entre les deux composants. Cette mémoire est nettement plus rapide que la RAM standard mais en faible quantité. Ce cache va garder en mémoire les suites d'instructions et données les plus utilisées et les renvoyer au microprocesseur à la demande. Au départ, deux types de cache vont être utilisés: le cache L1 (interne implanté dans le processeur) et le cache L2 (extérieur au processeur, puis intégré dans le même circuit et finalement complètement intégré dans l'architecture du processeur pour les modèles actuels). Le contenu des caches est mis à jour presque en temps réel.

Les

caches L1 sont intégrés directement dans le coeur du processeur, leur taille

est très faible mais les transferts sont directs. Actuellement, il est

découpé en deux parties: une pour les instructions (généralement

pré-décodées) et une pour les données.

Les

caches L1 sont intégrés directement dans le coeur du processeur, leur taille

est très faible mais les transferts sont directs. Actuellement, il est

découpé en deux parties: une pour les instructions (généralement

pré-décodées) et une pour les données.

Pour les 486, Pentium 1 et K6, la gestion du cache L2 utilise un circuit externe qui vérifie sur le bus d'adresse les plages mémoires les plus souvent chargées pour reprendre le contenu dans la mémoire tampon.

Le

Nexgen NX586,

sorti à peu prêt en même temps que le Pentium d'Intel, modifie radicalement

le positionnement. La mémoire cache n'est plus intégrée entre la Ram et le

processeur mais gérée indépendamment par un contrôleur intégré dans le

processeur. La mise en cache est plus intelligente et les bus de données

externes restent accessibles pour télécharger d'autres instructions quand le

processeur récupère des instructions enregistrées dans la mémoire tampon.

Le

Nexgen NX586,

sorti à peu prêt en même temps que le Pentium d'Intel, modifie radicalement

le positionnement. La mémoire cache n'est plus intégrée entre la Ram et le

processeur mais gérée indépendamment par un contrôleur intégré dans le

processeur. La mise en cache est plus intelligente et les bus de données

externes restent accessibles pour télécharger d'autres instructions quand le

processeur récupère des instructions enregistrées dans la mémoire tampon.

Intel

va reprendre le même principe avec le Pentium Pro mais en intégrant le cache

dans le même boîtier que le processeur: il devient finalement interne. Tous

les processeurs actuels utilisent cette architecture.

Intel

va reprendre le même principe avec le Pentium Pro mais en intégrant le cache

dans le même boîtier que le processeur: il devient finalement interne. Tous

les processeurs actuels utilisent cette architecture.

Dans les processeurs actuels, le cache L2 est entièrement repris dans l'architecture du processeur.

Les caches L3 sont apparus avec les K6-3 qui utilisaient un cache L2 géré en interne mais aussi un cache L2 d'ancienne génération (appelé L3). Actuellement, en multi-processeurs, les tampons L3 sont principalement utilisés comme liaisons entre les différents coeurs.

Ces deux caches amméliorent nettement les performances des processeurs: un CELERON 300 sans cache L2 n'atteint que 60% de performance part rapport à un Pentium II identique mais avec un cache L2 de 512K à la moitié de la fréquence du processeur.

7.3. Passage du CISC au RISC

La deuxième solution permettant d'augmenter les performances modifie l'architecture interne des microprocesseurs: en passant CISC (comme le 8088) au RISC. Les instructions enregistrées en mémoire restent compatibles mais sont prédécodées pour devenir des instructions RISC en interne spécifiques à chaque famille de processeurs. Les performances ne sont plus fonction de la fréquence mais de la structure de décodage et des performances internes.

| Avantages d'un processeur CISC: | Défauts d'un processeur CISC |

|

1. Instructions en assembleur plus proches d'un langage de programmation

standard comme le C

2. Moins de lignes de codes en mémoire pour le même programme 3. Ecriture des applications plus rapide, plus facile à lire et à comprendre |

1. beaucoup de codes différents pour les instructions

2. taille importante des instructions et variable (parfois supérieurs à 5 octets) 3. pas de standardisation des instructions (par exemple débuter par le même code hexadicimal toutes les instruction de chargement en mémoire): fonctionnement interne complexe et peu performant. |

|

Microprocesseur RISC |

|

|

|

Les processeurs modernes pour PC récupèrent en mémoire des instruction compatibles X86. Elles sont d'abord rangées en plusieurs cases sur 8 bits (plusieurs instructions à la suite des autres) puis converties en instructions RISC. Lorsqu'une d'elles est conditionnelle, il va devoir redemmander d'autres lignes de programme et réintroduire de nouvelles commandes CISC. Pour réduire ces problèmes, chaque microprocesseur utilise différentes méthodes: Intel intègre en amont de décodage un circuit de prédiction de branchement, AMD mémorise les derniers dans une table de branchement. En dernier, beaucoup d'instructions sont chargées avant le décodages et les valeurs peuvent aussi avoir été modifiées entre temps.

Le réel intérêt de ce décodage est l'implantation de circuits spécialisés par types d'instruction (y compris d'implanter un coprocesseur mathématique (nombres réels) directement dans la structure ou même d'exécuter plusieurs instructions de type différent simultanément. Ceci permet d'intégrer d'autres amméliorations, celle qui suivent.

7.4. Architecture pipeline, superpipeline et superscalaire

Dans les 8088-8086, le processeur ne commençait le traitement

d'une instruction que lorsqu'il avait complètement terminé la précédente. Une

architecture pipeline permet d'exécuter plusieurs

instructions simultanément. L'exécution d'une instruction en assembleur

est décomposée en 4 parties:

Dans les 8088-8086, le processeur ne commençait le traitement

d'une instruction que lorsqu'il avait complètement terminé la précédente. Une

architecture pipeline permet d'exécuter plusieurs

instructions simultanément. L'exécution d'une instruction en assembleur

est décomposée en 4 parties:

- chargement de l'instruction

- décodage

- exécution

- réponse à la commande

Dans

ce schéma, les bus externes ne sont utilisés que lors du chargement et lors de

la réponse (points 1 et 4). L'idée d'une architecture pipeline est

d'optimaliser l'utilisation des bus externes en chargeant l'instruction suivante

pendant le décodage de la précédante: trois instructions sont traitées

(presque simultanément).

Dans

ce schéma, les bus externes ne sont utilisés que lors du chargement et lors de

la réponse (points 1 et 4). L'idée d'une architecture pipeline est

d'optimaliser l'utilisation des bus externes en chargeant l'instruction suivante

pendant le décodage de la précédante: trois instructions sont traitées

(presque simultanément).

En super pipeline, l'exécution de l'instruction est maintenant découpée en 6 ou 7 parties:

- Chargement

- Deux décodages (le deuxième pourvant être omis pour des instructions simples)

- Deux calculs d'adresses (pouvant être omis dans certains cas)

- Exécution de la commande

- Renvoi du résultat.

Ceci n'augmente pas réellement le nombre d'instructions exécutées simultanément mais réduit le temps global d'exécution de chacune. Chaque fois qu'une des parties découpée n'est pas nécessaire, elle est omise, augmentant la vitesse d'exécution de la suivante.

Architecture superpipeline: Processeur CYRIX M1 avec architecture super-pipeline à 7 niveaux.

Architecture superscalaire

La structure superscalaire découle du décodage CISC - RISC et d'une architecture superpipeline. Une fois décodées, les instructions sont traitées par des unités spécialisées simultanément. L'Athlon, comme tous les processeurs actuels est superpipeline et super scalaire.

7.5. Technologie des transistors, alimentations.

A l'intérieur des processeurs et circuits périphériques, transistors utilisés sont des CMOS ou des BiCMOS: ces technologies permettent une intégration élevée à des fréquences relativement hautes mais surtout une faible consommation. Un autre avantage est lié à la tension d'alimentation (nommée V Core dans les notes technique) qui diminue avec les évolutions technologiques, réduisant la consommation et l'échauffement qu'elle provoque dans le circuit. Cette évolution permet également de réduire la taille de chaque transistor (et d'aumenter le nombre dans un même circuit. Réduire la taille permet de diminuer les distances parcourues par les signaux électriques, augmentant la vitesse et réduisant aussi la consommation du circuit.

Par exemple, les processeurs de 1995 étaient gravés en 0,5 micron (10-6) alors qu'un I7 de 2015 (sixième génération) est gravé en 14 nm (10-9), soit une réduction de plus de 35%. Un 486 était alimenté en +5 volts, un K6-3 ne nécessitait que 2,2 volts et un I7 pour portable utilise une alimentation variant suivant la charge de 0,55 à 1,52 volts.

7.6. Architecture interne des processeurs

Nous allons profiter de ce chapitre pour analyser le schémas interne de quelques processeurs. Prenons pour débuter un K5 d'AMD, 2,5 fois plus performant qu'un 486 à la même fréquence. Il est en RISC et superscalaire.

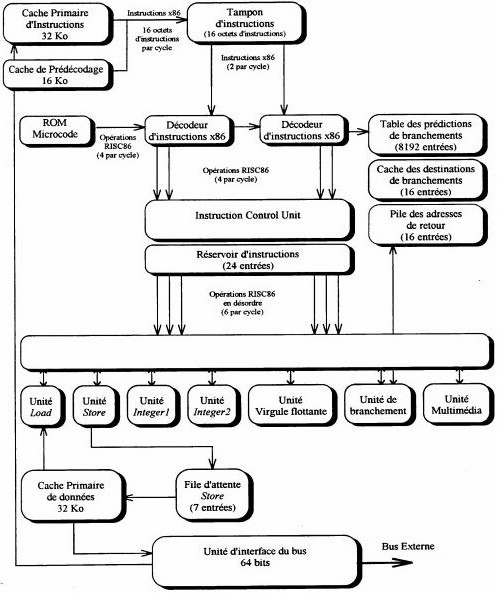

Schéma d'architecture générale d'un AMD K5

Dans la partie supérieur gauche, on retrouve un cache L1 dédié aux instructions instruction (le cache pour les données se trouve après l'exécution). Pour AMD, toutes les instructions chargées à partir de la mémoire transitent par ce cache. Un deuxième cache L1 lui est accouplé mais avec des instructions prédécodées suivant le type d'instructions. Ces deux parties communiquent avec un tampon d'instruction en envoyant 16 octets d'instructions par cycle d'horloge (d'où l'intérêt des caches puisque le bus de données d'un K5 est de 64 bits (8 octets). Les instructions CISC sont transmises à deux décodeurs qui travaillent en parallèle (4 instructions décodées par cycle d'horloge). Ces deux décodeurs sont remiés à une table de prédiction de branchement pour les instructions conditionnelles et à une ROM microcode reprenant la correspondance est les deux types d'instructions. Les instructions décodées sont ensuite renvoyés dans un tampon d'instruction sur 24 entrées. A partir de ce réservoir, les instructions sont envoyées vers les différentes unités de traitement internes (coprocesseur mathématique, instructions multimédia, instructions mémoires, ...) mais aussi vers un cache de destination de branchement (utilisé par les instructions conditionnelles). Les résultats sont enregistrés dans une file d'attende superpipeline sur 7 niveaux).

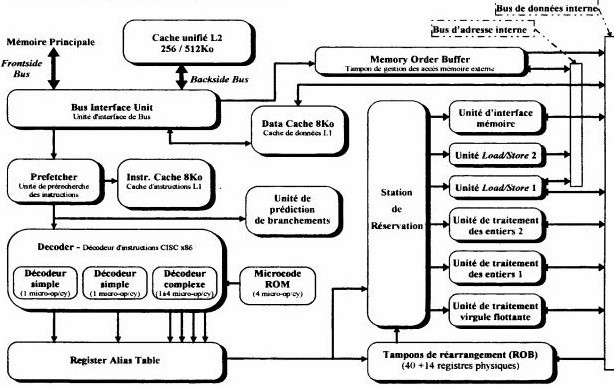

L'architecture interne d'un Pentium Pro est identique, sauf le cache L2 qui est externe. Les Pentium II et III utilisent la même.

Architecture générale d'un processeur Pentium Pro (identique au Pentium II et III).

7.7. Conclusion.

Ceci n'est qu'une simple introduction à l'architecture interne des processeurs modernes. Ceci modifie complètement la perception fréquence / performance et explique ques les athlons XP et Sempron n'affichent plus les fréquences utilisées mais associent leurs performances par comparaison avec les processeurs équivalents Intel. Les deux chapitres suivant reprennent des processeurs plus modernes et plus complexes. Pourtant, les structures actuelles sont de plus en plus allégées (notamment avec les processeurs ARM mais aussi en réduisant la taille du pipeline) mais en couplant plusieurs processeurs simultanément.

|

Processeurs

spécifiques pour

serveurs informatiquess. Les modèles qui sont spécifiques pour les serveurs réseaux. |

Remplacement d'un disque dur et récupération des données Remplacer le disque dur en récupérant les données de l'ancien. |

|

La suite sur la structure interne > 7.A AMD

64 bits (Athlon 64, Opetron, ...) 7.b. Netburst, Intel Core 8. Les chipsets |

| < 6. Bus PC: ISA, PCI, PCI-express, AGP, ... |

Révision: le 9/06/2008

Le cours hardware première année (PC et périphériques). Le cours Hardware deuxième année (réseaux, serveurs et communications)

Les compétences au service de la qualité.

Les activités d'YBET informatique à Pin (Chiny)

Mesure d'audience ROI frequentation par