7.a. Athlon 64 Structure

7.a.1. Introduction - 7.2. Structure standard of the athlon 64, 64 FX and Opteron - 7.a.3. Internal structure of Athlon 64

7.a.1. Introduction

In the preceding chapter, we have the internal architecture of standard processors. We will see in this chapter the architecture of Athlons 64 bits (also 64 FX and Opteron). Even if the heart of the processor seems equivalent, the various models differ mainly by their external components.

The athlon 64 in the general direction use a mixed internal architecture 32 - 64 bits. They are thus able to use operating systems 32 bits (Windows 95/98/me/2000/NT/XP) and operating system 64 bits (currently semi-2004: Linux even if a version Windows 64 bits is under development - specific versions Windows server).

Itanium of INTEL use only one architecture 64 bits, they can thus use only operating system 64 bits.

A processor 64 bits using an operating system 64 bits can jointly use applications 32 and 64 bits. On the other hand, case of the AMD, a processor 64 bits turning on an operating system 32 bits can make turn only of the applications 32 bits. Conversely, a processor 32 bits can use only operating systems and applications 32 bits.

A broad part of the information taken again on this page comes directly from the site of AMD

7.a.2. Structure standard of the athlon 64, athlon 64FX and Opteron

Let us begin with the standard architecture of an athlon 64 family. It consists of 2 parts: the processor part as we know and the part "Northbridge", in the past included in the chipset.

The L2 mask varies according to the processor: 256, 512 or 1 MB for Athlon 64, 1 MB for Athlon 64 FX51 and Athlon FX53 and Opteron.

In the part "Northbridge", one will find the interface memory DDR. It is the first difference between different the processor from the family 64 bits from AMD. Athlon 64 manage an external data bus of 64 bits, the FX and Opteron of the data buses of 128 Bits. As these processors manage memories ECC, Athlon 64 bits will accept memory ECC on 8 bits of control against 16 bits-ECC for the others. The socket processor is thus different for the 64 and 64 FX

Part JTAG - Debug is related to the difficulty in testing complex electronic circuits. This developed method fine of the Eighties makes it possible to test "outside" the electronic circuit by memorizing the values of entries and exits. It thus is not directly used in the PC.

Hyper transport is the fast bus allowing connection between northbridge and Southbridge. The number of channels is 1 for Athlon 64 and Athlon 64FX. For the opteron, it is of 3 channels. Each channel is able to transfer 3,2 GB/s in each direction (6,4 GB/s on the whole).

All this explains in particular different the socket for the family Athlon 64

Athlon 64: socket 754, advanced mid- 2004 towards the socket 939 which manages Dual Channel

Athlon 64 FX: socket 940 (identical to the opteron), advanced mid- 2004 towards the socket 939 (identical to Athlon64). First Athlon FX51 were thus of Opteron with 2 of the three channels hyper decontaminated transport. Athlon FX53 becomes again Athlon 64 (which it replaces) with a more important mask.

Athlon Opteron: socket 940

7.a.3. Structure intern of Athlons 64

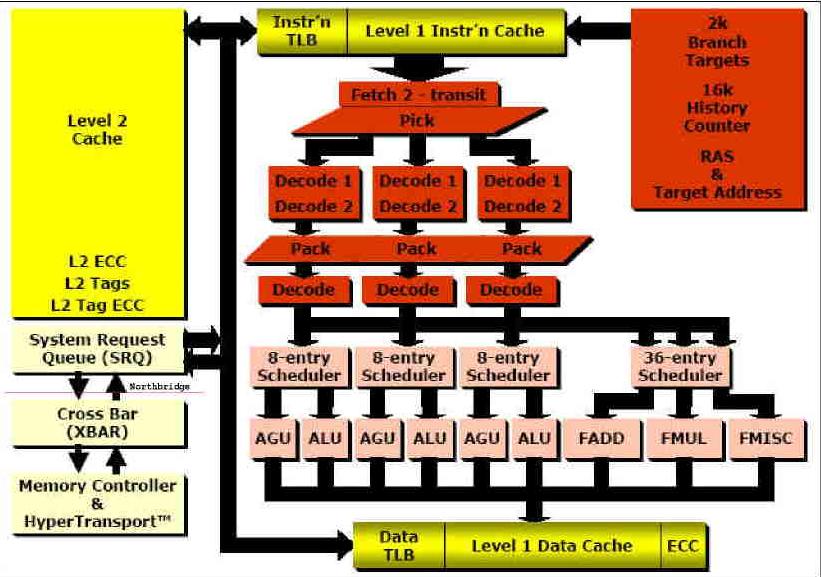

The architecture of Athlon 64 is not is a revolutionist. The data are sent and received memory via the controller Hyper-transport and controller report on the left. They are sent either the reserve of instruction. The mask of L1 instructions connected to the circuit of prediction of connection also makes it possible to provide instructions to the processor.

The part in red gathers the decoding of the CISC towards RISC with 3 levels of decoding. The various parts intern are not deferent processors which we know: calculating units ALU, AGU (Address Generation Links) for calculations on addresses, FADD (calculating unit in floating point)...

The data are then returned either towards the L1 mask corresponding, or towards the memory.

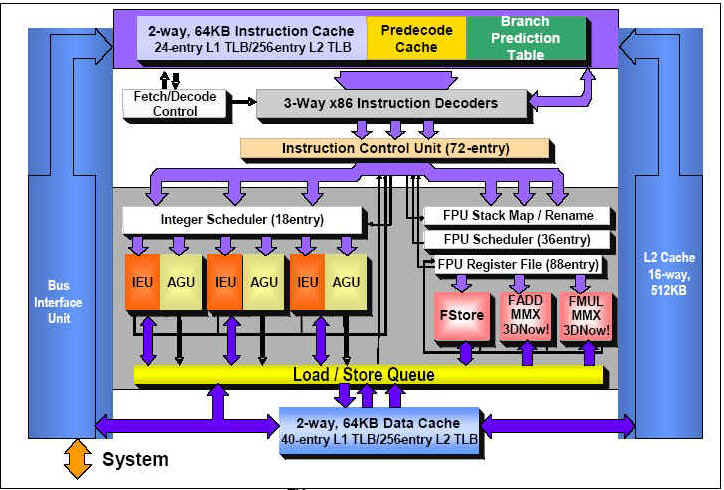

In a direction, the internal architecture of Athlon 64 (pink) is not very different from that of Athlon XP

Internal structure for Athlon XP

One finds the new ones on a side drank it of order, data and addresses (Drunk Interface Links) and the data coming from the L2 mask (included in the processor). The part above is used for predecode the instructions and includes the table of prediction of connection. The following part gathers the passage of instructions CISC towards RISC and the transfer towards the various internal units of Athlon XP.

| The continuation of the course hardware 1 > 8. Chipset PC |

Computer equipment 1: PC and peripherals. Computer equipment 2: networks, servers and communication

Competences with the service of quality in data-processing.